#### OpenFPGA CoreLib Core Library Interoperability Effort

M. Wirthlin<sup>1</sup>, D. Poznanovic<sup>2</sup>, P. Sundararajan<sup>3</sup>, A. Coppola<sup>4</sup>, D. Pellerin<sup>5</sup>, W. Najjar<sup>6</sup>, R. Bruce<sup>7</sup>, M. Babst<sup>8</sup>, O. Pritchard<sup>9</sup>, P. Palazzari<sup>10</sup>, G. Kuzmanov<sup>11</sup>

<sup>1</sup>Brigham Young University, <sup>2</sup>SRC Computers, <sup>3</sup>Xilinx Corporation, <sup>4</sup>OptNgn Software, <sup>5</sup>Impulse, <sup>6</sup>UC Riverside, <sup>7</sup>Nallatech, <sup>8</sup>DSPLogic, <sup>9</sup>Altera Corporation, <sup>10</sup>Ylichron, <sup>11</sup>TU Delft

#### Overview

- Background and Motivation

- OpenFPGA CoreLib Project Goals

- Related Hardware Circuit Reuse Efforts

- XML & IP-XACT

- Example

- Status and Future Work

# FPGA Design Methods

- Register Transfer Level

VHDL, Verilog, etc.

- "Low-Level" Circuit Design

- Focus on implementation

- Time consuming

- High quality circuits

- High Performance

- Meet timing constraints

- Meet resource constraints

- Utilized specialized resources

#### HLL

- High-Level Languages

- C, C++, Java, SystemC, etc.

- Graphical Programming

- "High-Level" Algorithm Design

- Focus chalgorithm

- Implementation details ignored

- Possibly lower quality circuits

- High Productivity

- Easy to modify algorithm

- Fewer Implementation details

- Less design time

#### High Performance "Cores"

- High-performance circuit "cores" needed for highperformance

- Perform performance critical functions (FFT, etc.)

- Hand crafted, efficient implementations

- Manage a complex resources (MGT, memories, etc.)

- Cores often described in "low-level" language

- VHDL, EDIF, raw bitstreams, etc.

- Provide high-performance, hand crafted circuit "functions"

# High Performance "Cores"

- High-performance circuit "cores" needed for highperformance

- Perform performance critical functions (FFT, etc.)

- Hand crafted, efficient implementations

- Manage a complex resources (MGT, memories, etc.)

- Cores often described in "low-level" language

- VHDL, EDIF, raw bitstreams, etc.

- Provide high-performance, hand crafted circuit "functions"

- Challenge:

- How do we integrate high-performance cores into high-level languages?

- How do we reuse high-performance cores with more than one high-level language?

#### **Project Goals**

- 1. Develop a standard for circuit cores

- 2. Develop a standard for circuit libraries

- 3. Encourage the use of these standards

- 4. Create a synergistic environment

- 5. Create Libraries

**RSSI 2007**

#### Hardware Reuse

- Reuse of hardware circuits is very important for hardware engineers

- Reduce design cost of large single chip systems

- Amortize cost of circuit cores over multiple chips

- Purchase high-quality circuits from "IP" specialists

- Hardware reuse is more difficult than software reuse

- Complex interfaces

- Signal timing, signal types, communication protocol

- Physical implications

- Circuit area, timing, power, placement, etc.

- Challenging verification

- How do you know it works?

#### Hardware Reuse Efforts

#### opencores.org

- Open source repository of circuit cores

- Cores developed for wishbone bus interface

- Specifies a common standard for core interface

- Proviles tools/infrastructure for integrating cores

- **SPIRIT** Consortium

- Develops specs for *describing* circuits for re-use

- Created IP-XACT v1.2 spec (used in this work)

- VSI Virtual Socket Interface Alliance (VSI)

- Provide standards, docs, and methods for SoC design

- Facilitate circuit protection and transfer

- Si<sub>2</sub>

- Facilitate interoperability of EDA tools

- Provides common libraries and interoperability tools

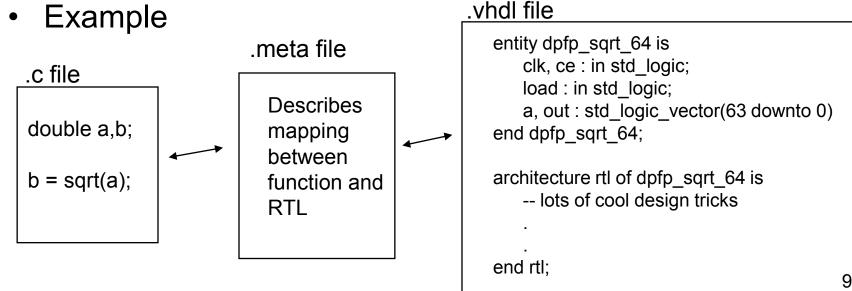

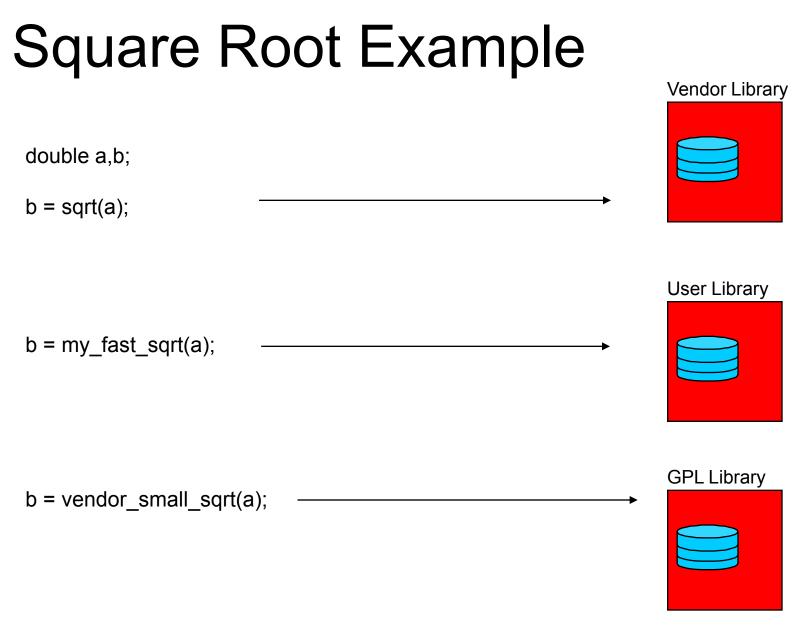

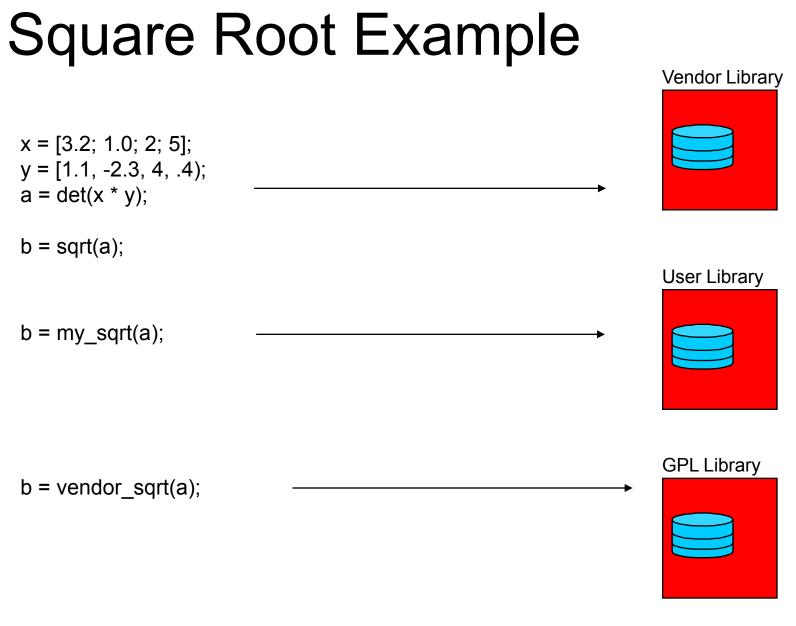

# Reuse with Existing HLL Tools

- Techniques used for importing external cores

- Function call interface

- New language semantics or PRAGMA statements

- Overloading standard operators

- New graphical library elements

- Custom instructions

**RSSI 2007**

# Reuse with Existing HLL Tools

- Techniques used for importing external cores

- Function call interface

- New language semantics or PRAGMA statements

- Overloading standard operators

- New graphical library elements

- Custom instructions

- Commercial

- Impulse-C

- Dime-C

- Carte

- Research

- ROCCC

– CHIMPS

- Trident

- DWB

- Reconfigurable Computing Toolbox

- C2H

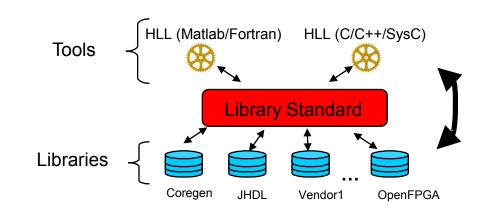

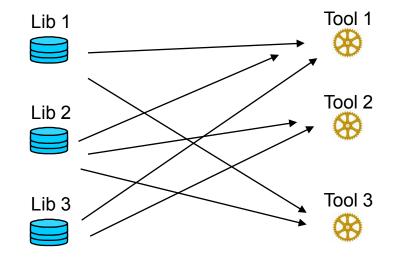

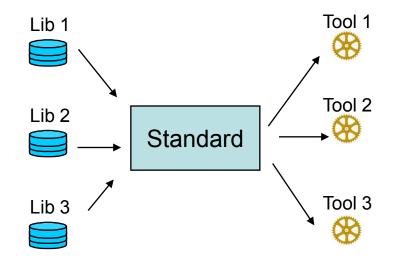

#### **Reuse Challenges**

- Each tool has a custom method for importing core

- Importing external core for new tool requires extra work

- Difficult to use same core in multiple tools

- Difficult to reuse libraries among tools

#### Reuse Goal

- Each core and library conforms to a standard

- Each tool recognizes this standard

- Easy to use same core in multiple tools

- Easy to reuse libraries among tools

#### **IP Interface Standard Requirements**

- Structural Information

- Signals (name, bit width, properties)

- Signal types (higher level type information)

- Timing Interface

- Signal arrival times

- Signal response times

- Control interface

- Interface protocol specification

- Handshaking requirements

- Parameterization

- Estimation interface

- External tool/generator interface

# XML Circuit Meta Description

- Exploit XML infrastructure to describe cores and libraries

- Define custom XML schema for describing cores

- Create XML descriptions of reusable cores

- Define all details of complicated circuit interface

- Provide multiple views of core

- Package cores into reusable libraries

- Benefits

- Many tools available for manipulating/viewing XML

- Several HLL tools already use XML to describe cores

- Existing techniques for publishing cores with XML (IP-XACT)

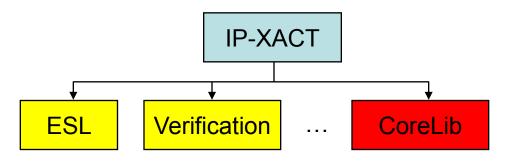

#### **IP-XACT**

- XML meta description of reusable IP

- XML schema defining tags for specifying reusable IP

- Defines interface, configuration, and generation of IP

- Used primarily for defining bus-based IP in SoC design

- Current standard intended for RTL-level IP

- Created by the Spirit Consortium

- Non-profit organization with over 60 company members

- Led primarily by ARM and Mentor Graphics

- Being considered as an IEEE Standard (P1685)

- Compatible and complementary with other IP-reuse activities

- Opencores, OCP-IP, etc.

#### Example – UART on AMBA Bus

<spirit:component xmlns:spirit="http://www.spiritconsortium.org/XMLSchema/SPIRIT/1.2" xmlns:xsi="http://www.w3.org/2001/XMLSchema-i

```

Raw XML

```

e" xsi:schemaLocation="http://www.spiritconsortium.org/XMLSchema/SPIRIT/1.2 Y:\SCHEMA~2\V1.2\index.xsd"> <spirit:vendor>spiritconsortium.org</spirit:vendor> <spirit:library>Leon2</spirit:library> <spirit:name>uart</spirit:name> <spirit:version>1.2</spirit:version> <spirit:busInterfaces> <spirit:busInterface> <spirit:name>APBClk</spirit:name> <spirit:busType spirit:vendor="AMBA" spirit:library="AMBA2" spirit:name="APB" spirit:version="rOpO"/> <spirit:system> <spirit:group>APB CLK</spirit:group> </spirit:system> <spirit:connection>required</spirit:connection> <spirit:signalMap> <spirit:signalName> <spirit:componentSignalName>clk</spirit:componentSignalName> <spirit:busSignalName>PCLK</spirit:busSignalName> </spirit:signalName> </spirit:signalMap> </spirit:busInterface> <spirit:busInterface> <spirit:name>APBReset</spirit:name> <spirit:busType spirit:vendor="AMBA" spirit:library="AMBA2" spirit:name="APB" spirit:version="r0p0"/> <spirit:system> <spirit:group>APB RESET</spirit:group> </spirit:system> <spirit:connection>required</spirit:connection> <spirit:signalMap> <spirit:signalName> <spirit:componentSignalName>rst</spirit:componentSignalName> <spirit:busSignalName>PRESETn</spirit:busSignalName> </spirit:signalName> </spirit:signalMap> </spirit:busInterface> <spirit:busInterface> <spirit:name>ambaAPB</spirit:name> <spirit:busType spirit:vendor="AMBA" spirit:library="AMBA2" spirit:name="APB" spirit:version="r0p0"/> <spirit:slave> <spirit:memoryMapRef spirit:memoryMapRef="ambaAPB"/> </spirit:slave> <spirit:connection>required</spirit:connection> <spirit:signalMap> <spirit:signalName> <spirit:componentSignalName>psel</spirit:componentSignalName> <spirit:busSignalName>PSELx</spirit:busSignalName> </spirit:signalName> <spirit:signalName> <spirit:componentSignalName>penable</spirit:componentSignalName>

#### Example – UART on AMBA Bus

| -                         | ,                                                                                |                              |

|---------------------------|----------------------------------------------------------------------------------|------------------------------|

| 🗉 🖻 spirit:component      |                                                                                  |                              |

|                           | http://www.spiritconsortium.org/XMLSchema/SPIRIT/1.2                             |                              |

|                           | http://www.w3.org/2001/XMLSchema-instance                                        |                              |

|                           | http://www.spiritconsortium.org/XMLSchema/SPIRIT/1.2口口Y:\SCHEMA~2\V1.2\index.xsd |                              |

| e spirit:vendor           | spiritconsortium.org                                                             |                              |

| 🖻 spirit:library          | Leon2                                                                            |                              |

| 🖻 spirit:name             | uart                                                                             |                              |

| spirit:version            | 1.2                                                                              |                              |

| 🗉 🖻 spirit:busInterfaces  |                                                                                  |                              |

| 🗉 🖻 spirit:busInterface   |                                                                                  |                              |

| 🗉 🖻 spirit:busInterface   |                                                                                  | Eclipse IP-XACT Plug-In View |

| 🗉 🖻 spirit:busInterface   |                                                                                  |                              |

| 🖻 spirit:name             | ambaAPB                                                                          |                              |

| 🗉 📧 spirit:busType        |                                                                                  |                              |

| 🗉 📧 spirit:slave          |                                                                                  |                              |

| spirit:connection         | required                                                                         |                              |

| 🗉 📧 spirit:signalMap      |                                                                                  |                              |

| 🗉 📧 spirit:signalName     |                                                                                  |                              |

| 🗉 📧 spirit:signalName     |                                                                                  | Several tools available for  |

| 🗉 📧 spirit:signalName     |                                                                                  |                              |

| spirit:componentSignalN   | 2 paddr                                                                          | manipulating and greating    |

| 📧 spirit:busSignalName    | PADDR                                                                            | manipulating and creating    |

| 🗉 📧 spirit:signalName     |                                                                                  | ID VACT moto departintions   |

| 🖻 spirit:componentSignalN | ۶ pwrite                                                                         | IP-XACT meta descriptions    |

| 📧 spirit:busSignalName    | PWRITE                                                                           |                              |

| 🖃 📧 spirit:signalName     |                                                                                  |                              |

| 🖻 spirit:componentSignalN | 2 pwdata                                                                         |                              |

| 📧 spirit:busSignalName    | PWDATA                                                                           |                              |

| 🖃 📧 spirit:signalName     |                                                                                  |                              |

| 🖻 spirit:componentSignalN | 2 prdata                                                                         |                              |

| 🖻 spirit:busSignalName    | PRDATA                                                                           |                              |

| 🗉 🖻 spirit:busInterface   |                                                                                  |                              |

| 🗉 🖻 spirit:memoryMaps     |                                                                                  |                              |

| 🗉 🖻 spirit:memoryMap      |                                                                                  |                              |

| 🖻 spirit:name             | ambaAPB                                                                          |                              |

| 🗉 🖻 spirit:addressBlock   |                                                                                  |                              |

| 🗉 🖻 spirit:model          |                                                                                  |                              |

|                           |                                                                                  |                              |

#### **IP-XACT** Extensions

- IP-XACT standard not sufficient for CoreLib effort

- Limited to bus-based cores and HDL data types

- Limited support for custom interfaces

- IP-XACT supports a variety of *extensions* for new functionality

- Develop extensions to IP-XACT for CoreLib

- Higher level data types (floating point, fixed point, etc.)

- Temporal interface (timing and protocol)

- Specifying behavior (arithmetic functions)

- Advanced memory architectures

**RSSI 2007**

**RSSI 2007**

#### Status

- Completed survey of previous work

- Gathered information about tools

- Proposed framework around IP-XACT

- Experimenting with IP-XACT

- Gathering freely available cores

#### Future Work

- Develop sample IP-XACT wrappers for cores

- Propose and demonstrate extensions

- Solicit feedback from vendors

- Encourage use of standards

## CoreLib Wiki

https://isl.ncsa.uiuc.edu/twiki/bin/view/OpenFPGA/CoreLib

- Related Circuit Reuse Activities

- Tools and Compilers

- Examples

- HLL Compiler Requirements

- Interface Standards